低功耗集成电路设计领域传来振奋人心的消息。随着半导体工艺不断向更小节点迈进,功耗问题已成为制约高性能芯片发展的关键瓶颈之一。针对这一挑战,国内外研究团队在多条技术路线上取得了一系列突破性进展,为实现更高效能、更长续航的下一代电子设备奠定了坚实的基础。

传统集成电路的功耗主要由动态功耗和静态功耗两部分构成。在动态功耗方面,研究人员通过创新性的电路架构设计,如采用异步电路、近阈值电压计算以及动态电压频率调节(DVFS)等技术,显著降低了晶体管在开关过程中产生的能耗。其中,一种基于事件驱动型的异步逻辑设计,能够仅在需要时激活相应电路模块,避免了全局时钟信号带来的冗余功耗,在特定应用场景下实现了能效的成倍提升。

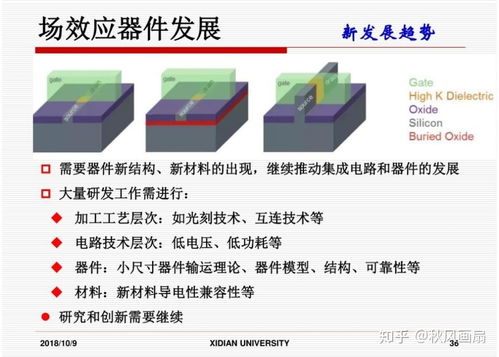

在静态功耗,即漏电流功耗的管理上,进展同样显著。随着晶体管尺寸微缩,漏电流问题日益突出。新型高K金属栅极技术、鳍式场效应晶体管(FinFET)乃至更先进的环栅晶体管(GAA)结构,从物理层面有效抑制了漏电流。在电路设计层面,多阈值电压技术、电源门控以及体偏置技术的智能运用,使得芯片能够在高性能模式和超低功耗待机模式之间灵活切换,大幅延长了物联网传感器、可穿戴设备等产品的电池寿命。

系统级与算法层面的协同优化是另一大亮点。研究者们不再局限于单个晶体管或逻辑门的功耗优化,而是将芯片视为一个整体系统。通过硬件与软件的深度融合,例如设计专用的低功耗人工智能加速器、采用稀疏计算来避免不必要的操作,以及开发能感知任务负载并动态调整资源配置的智能管理单元,从系统顶层实现了功耗的精细化管控。

这些研究成果正逐步从实验室走向产业应用。在移动通信、边缘计算、生物医疗植入设备和无处不在的物联网节点等领域,低功耗芯片已成为刚性需求。本次取得的进展,不仅意味着未来我们的手机、智能手表一次充电可以使用更久,更预示着那些部署在偏远地区或人体内部的设备,其维护周期将被极大延长,可靠性得到质的飞跃。

尽管挑战依然存在,例如在极低电压下电路稳定性的保障、先进工艺带来的设计复杂性激增等,但此次多方面的研究进展无疑为整个行业注入了强劲动力。低功耗集成电路设计,正朝着更高能效、更智能化的方向稳步前行,悄然推动着一场静悄悄的绿色计算革命。