模数转换器作为连接模拟世界与数字系统的桥梁,在现代电子设备中扮演着核心角色。其应用电路的设计质量,直接决定了整个系统的性能、精度与可靠性。从集成电路设计的角度看,ADC应用电路的设计是一个系统工程,需兼顾架构选择、外围电路匹配、噪声抑制与电源完整性等多方面因素。

一、ADC架构选择与系统需求匹配

集成电路设计的第一步是根据系统需求选择合适的ADC架构。高速应用如通信接收机,常采用流水线型或闪存型ADC,以满足高采样率需求;而对于高精度测量仪器,Σ-Δ型ADC凭借其出色的噪声整形能力和高分辨率成为首选;低功耗嵌入式系统则多采用逐次逼近型ADC。设计者需在速度、精度、功耗和芯片面积之间做出权衡,此选择是后续电路设计的基础。

二、关键外围电路设计要点

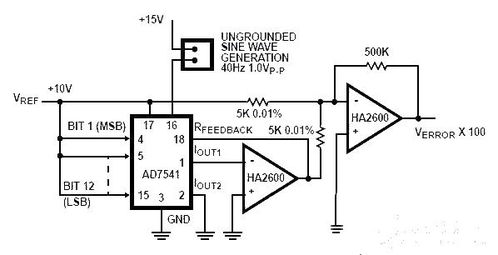

- 模拟前端与驱动电路:ADC之前的模拟信号调理电路至关重要。需要设计高性能的运算放大器驱动电路,确保信号在ADC的输入范围内,并具有足够的建立时间和驱动能力。驱动运放的带宽、压摆率、噪声特性必须与ADC匹配,避免引入失真或限制动态性能。对于全差分输入ADC,通常需要配置差分驱动电路,并注意共模电平的精确设置。

- 基准电压源设计:基准电压的稳定性直接决定ADC的转换精度。在芯片内部,需要设计低噪声、高精度、低温漂的带隙基准电压源。外部基准引脚通常需要连接高质量的去耦电容,以滤除噪声并提供瞬时电流。对于高精度ADC,甚至需要考虑使用外部独立基准源,并设计精密的分压或缓冲电路。

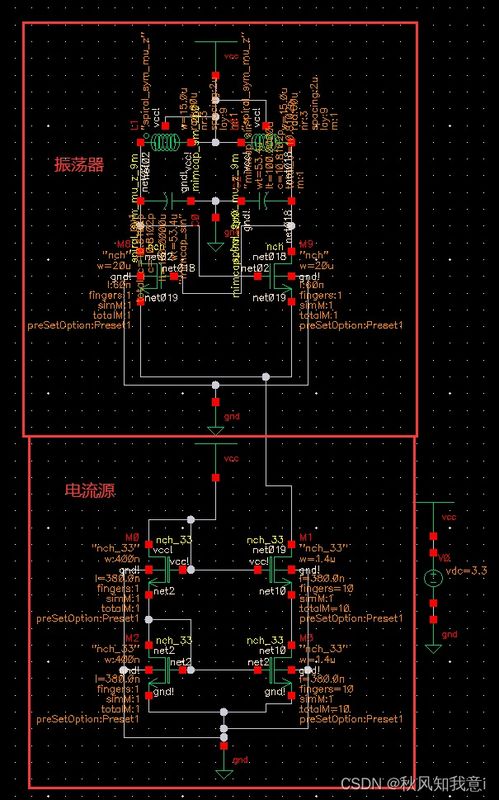

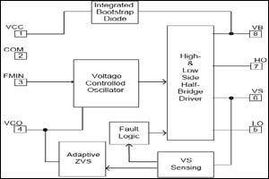

- 时钟电路与采样保持:采样时钟的相位噪声和抖动是影响ADC信噪比和动态范围的关键因素。在IC设计中,需采用低抖动的时钟生成电路(如PLL),并对时钟路径进行精心布局布线,减少串扰。采样保持电路的设计则需保证在采样窗口内快速精确地捕获输入信号,其开关的非线性、电荷注入效应都需要通过电路技术(如bootstrapped开关)进行补偿和优化。

三、噪声抑制与电源完整性设计

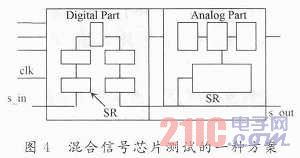

混合信号集成电路设计的最大挑战之一是数字噪声对敏感模拟电路的干扰。

- 电源分离与滤波:在芯片版图层面,模拟电源(AVDD)与数字电源(DVDD)通常需要独立的引脚和内部布线。每个电源引脚附近都需要集成或外接高质量的去耦电容,形成低阻抗回路,以吸收高频噪声。电源稳压器的选择与设计也需考虑噪声特性。

- 接地策略与版图布局:采用星型接地或平面分割接地策略,确保数字电流的大幅度波动不会在模拟地线上产生压降。在版图设计上,模拟模块与数字模块应物理隔离,敏感模拟走线(如基准、时钟、输入信号)需远离高速数字信号线,并采用保护环(Guard Ring)等技术进行屏蔽。

- 数字接口隔离:ADC输出端的高速数字接口(如SPI、并行或LVDS)是主要的噪声源。设计中可采用锁存器进行信号同步,并使用独立的IO电源。在数字输出驱动器与核心模拟电路之间,插入缓冲器或采用电流隔离技术,能有效防止数字开关噪声回灌至模拟域。

四、性能验证与校准电路集成

先进的ADC集成电路通常集成自校准或后台校准功能,以补偿制造工艺偏差、温度漂移等引起的误差。设计时需预留校准DAC、比较器逻辑等电路模块。需设计有效的测试模式,以便在生产测试中快速评估ADC的静态参数(DNL、INL)和动态参数(SNR、SFDR)。

模数转换器应用电路设计,在集成电路层面是一个深度耦合的系统工程。它超越了单纯的ADC核心电路设计,延伸至与之协同工作的完整信号链和电源管理系统的构建。成功的ADC应用设计,要求工程师深刻理解ADC的工作原理、系统需求以及混合信号设计的艺术,通过精心的架构规划、电路设计与版图实现,最终在硅片上达成性能、功耗与成本的完美平衡。